3

# Enhancement-mode double-top-gated metal-oxide-semiconductor nanostructures with tunable lateral geometry

E. P. Nordberg, <sup>1,2</sup> G. A. Ten Eyck, <sup>1</sup> H. L. Stalford, <sup>1,3</sup> R. P. Muller, <sup>1</sup> R. W. Young, <sup>1</sup> K. Eng, <sup>1</sup> L. A. Tracy, <sup>1</sup> K. D. Childs, <sup>1</sup> J. R. Wendt, <sup>1</sup> R. K. Grubbs, <sup>1</sup> J. Stevens, <sup>1</sup> M. P. Lilly, <sup>1</sup> M. A. Eriksson, <sup>2</sup> and M. S. Carroll <sup>1</sup> Sandia National Laboratories, Albuquerque, New Mexico 87123, USA <sup>2</sup>University of Wisconsin—Madison, Madison, Wisconsin 53706, USA <sup>3</sup>University of Oklahoma, Norman, Oklahoma 73019, USA (Received 9 June 2009; revised manuscript received 29 July 2009; published 29 September 2009)

We present measurements of silicon (Si) metal-oxide-semiconductor (MOS) nanostructures that are fabricated using a process that facilitates essentially arbitrary gate geometries. Stable Coulomb-blockade behavior showing single-period conductance oscillations that are consistent with a lithographically defined quantum dot is exhibited in several MOS quantum dots with an open-lateral quantum-dot geometry. Decreases in mobility and increases in charge defect densities (i.e., interface traps and fixed-oxide charge) are measured for critical process steps, and we correlate low disorder behavior with a quantitative defect density. This work provides quantitative guidance that has not been previously established about defect densities and their role in gated Si quantum dots. These devices make use of a double-layer gate stack in which many regions, including the critical gate oxide, were fabricated in a fully qualified complementary metal-oxide semiconductor facility.

DOI: 10.1103/PhysRevB.80.115331 PACS number(s): 73.63.Kv, 73.40.Qv

## I. INTRODUCTION

Depletion-mode lateral quantum dots in GaAs/AlGaAs heterostructures have been used to make electrically controlled spin qubits. 1-6 Important features of the lateral geometry include a tunable tunnel-barrier opacity, a highly tunable electron occupation, and an open active region, providing the ability to tune the position of the quantum dots. <sup>7–9</sup> The lateral noncollinear geometry helps to maintain strong tunnel coupling to two different reservoirs as quantum dots decrease in size. This geometry has been used to enable one-electron occupation in single, 10 double, 11 and triple quantum dots. 12 Charge sensor integration in these structures is also facilitated by the lateral open geometry and it assists in unambiguous identification of single electron occupation and spin measurement through spin-to-charge transduction. An additional aspect of the GaAs/AlGaAs material system is that all the nuclei have nonzero spin. Although the nuclear spins of both Ga and As have been used successfully to drive rotations in a singlet-triplet qubit, 13 and can be partially controlled, 14 nuclear spins are also an undesirable source of spin decoherence.

The existence of nuclear-spin-free semiconductor materials such as <sup>28</sup>Si has motivated significant efforts to realize silicon quantum-dot qubits. <sup>15–17</sup> Quantum dots have been formed in silicon by a wide variety of methods, including enhancement-mode silicon metal-oxide semiconductor (MOS) structures, <sup>18–20</sup> strained Si/SiGe (sSi/SiGe) modulation-doped heterostructures, <sup>21–25</sup> collinear gated nanowires, <sup>26</sup> and atomically patterned delta layers. <sup>27</sup> The ability to form few electron singlet and triplet states has also been demonstrated with spin-blockaded transport for both sSi/SiGe (Ref. 28) and enhancement-mode collinear MOS (Ref. 29) double quantum dots.

Advantages of pursuing enhancement-mode MOS structures include: (1) highly variable electron density in the twodimensional electron gas (2DEG); (2) the possibility for outstanding charge stability;<sup>30–32</sup> (3) simpler integration with standard classical Si complementary MOS (CMOS) electronics for potential integration with high-speed charge-sensing circuitry;<sup>33</sup> and (4) potential hybrid integration with single donors.<sup>34,35</sup> Investigation of enhancement-mode devices is further motivated by the recognition that charge noise in modulation-doped heterostructures, while very small, is in fact associated with the modulation doping layer that is absent in an enhancement-mode device.<sup>36</sup>

A common characteristic of silicon MOS enhancementmode quantum dots, to date, is that both the leads and the quantum dot(s) are collinear, with entrance and exit point contacts aligned across the device. 18-20,29-32 This geometry encourages the dot to form in a small region with only modest flexibility available to tune the quantum-dot position with respect to its leads, other neighboring quantum dots, and disorder in the system. In contrast, the gate designs most commonly used to form quantum dots in modulation-doped heterostructures have a more open gate pattern and a noncolinear design. <sup>10</sup> In such open designs, in part because electrons are not confined to a narrow strip by etching or a narrow top gate, many properties of the device are more easily tuned in situ, including the position of the dot and the role of any particular gate, a feature that helps explain the ubiquity of this design. Demonstration of an open noncollinear lateral MOS quantum-dot geometry with single-period Coulomb blockade, consistent with the lithographic gate geometry and not dominated by the period of localized parasitic dots, would lead to a significant increase in flexibility of enhancement-mode MOS quantum dots and would represent a critical step toward advancing the MOS system along the same path used for spin qubits in GaAs/AlGaAs.

Disorder is produced by many factors and the implications of the different forms of disorder for tunable quantumdot behavior are not well characterized or understood. The MOS system is susceptible to fabrication-induced disorder, which can manifest as scattering and parasitic dot formation

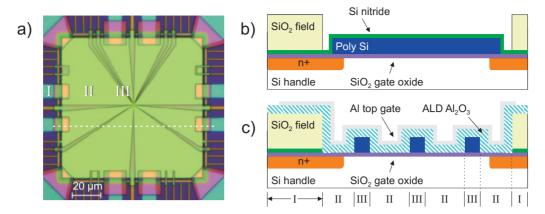

FIG. 1. (Color) (a) Optical image of an etch-defined device before both secondary dielectric and global top-gate deposition. The following features are identified: (I) *n*+implanted ohmic contacts extending into a window etched into the deposited field oxide, (II) exposed gate oxide within the etched oxide window, and (III) etched polysilicon gates patterned with electron-beam lithography. (b) Cross-sectional schematic after processing in the CMOS facility. (c) Cross-sectional schematic of the completed layer structure corresponding to the line cut indicated by the dashed horizontal line in (a).

in transport, making it difficult to probe only the transport resulting from the lithographically gated quantum dot. 35,37 One such factor is the introduction of charge defects. The density of such defects is a strong function of the device processing in MOS systems. Although there is an extreme wealth of knowledge about (a) silicon processing, (b) processing effects in classical room-temperature field-effect transistors (FETs), and (c) some studies on collinear quantum-dot geometries, 37,38 significant questions still remain about the implications the defects and disorder have for the viability of MOS quantum dots for coherent few electron-spin physics. A necessary step toward addressing these questions is to examine quantum-dot behavior with a fully characterized process flow.

In this paper we present (1) open-lateral MOS quantumdot transport that shows single-period Coulomb blockade over wide bias ranges; (2) single-period Coulomb blockade consistent with a quantum dot defined by the lithographic features and not dominated by disorder; (3) quantitative characterization of the process steps used to fabricate both the low disorder quantum dots as well as cases for which disordered quantum-dot behavior is strongly exhibited; and (4) numeric calculations of the corresponding magnitude of the disorder potential produced by these ranges of charge defects, which is compared to a modulation-doped GaAs/ AlGaAs case. An important contribution of this paper, therefore, is to demonstrate single-period, low disorder Coulomb blockade in an open MOS quantum-dot geometry and identify a quantitative range of defect density and mobility for which this behavior occurs.

The paper is divided into three sections. In Sec. I C, we describe the device design and fabrication including the use of an initial MOS stack fabricated within a 0.35  $\mu$ m CMOS production line that allows for flexible nanostructure post-processing. Defect characterization is described for critical nanostructure fabrication steps and includes mobility, interface trap density  $D_{\rm it}$ , and effective fixed-oxide charge  $Q_{\rm fb}$ . In Sec. I B, we report transport measurements of point contacts and quantum dots, including disorder free transport through devices with an open-lateral geometry. Section I C discusses

numerical calculations of both the disorder potential and the capacitance of a quantum dot using a three-dimensional (3D) finite element commercial package that shows that the measured quantum-dot capacitances are consistent with dots defined by the lithographic gates and not by a disorder potential.

## A. Device fabrication

The silicon quantum devices studied here are fabricated in two phases. A MOS gate stack with an exposed  $100~\mu m \times 100~\mu m$  degenerately doped polysilicon accumulation gate is fabricated using the same process line used for dedicated 350 nm CMOS circuit fabrication at Sandia National Laboratories. The gate stack is modified to allow a second phase of fabrication using electron-beam lithography (EBL), which is available only outside of the Si CMOS facility. These modifications include a window in the field oxide opened to expose the polysilicon for subsequent nanofabrication and peripheral  $n^+$  ohmic implants, providing electron reservoirs at the edge of the window, as seen in Figs. 1(a) and 1(b). Details of the phase I processing can be found in Appendix A.

The phase II fabrication of the nanostructure consists of EBL followed by a plasma etch to form the polysilicon depletion gates. A secondary dielectric, consisting of 60 nm of Al<sub>2</sub>O<sub>3</sub>, was added via atomic layer deposition (ALD), which was then annealed in forming gas. In some cases, reoxidation was done before the ALD step. Subsequent metallization for the top gate and its contacts were done to complete the structure, followed by a final forming-gas anneal. A schematic of the final gate stack can be seen in Fig. 1(c). Specific details of each step during phase II processing can also be found in Appendix A.

The disorder potential at the oxide-Si interface is influenced by a number of factors, including fixed defect charges within the oxide, interface trap charge, and surface roughness. Many processing steps in phase II can introduce damage resulting in additional charge within the structure and reducing the quality of the phase I material. Processing steps

| Condition                                       | T <sub>SiO2</sub> (nm) | T <sub>Al2O3</sub> (nm) | $\mu_{ m peak} \ ({ m cm^2/Vs})$    | Start $\mu_{\text{peak}}$ (cm <sup>2</sup> /Vs) | $n_{ m peak}$ (cm <sup>-2</sup> ) | $\mu(n=5\times10^{11} \text{ cm}^{-2})$<br>(cm <sup>2</sup> /Vs) | Density<br>method      | Oxidation condition          |

|-------------------------------------------------|------------------------|-------------------------|-------------------------------------|-------------------------------------------------|-----------------------------------|------------------------------------------------------------------|------------------------|------------------------------|

| Phase I only                                    | 35                     | 0                       | 8000–16 000<br>(wafer<br>dependent) | 8000–16 000                                     | ~10 <sup>12</sup>                 | 5500–10000                                                       | $C_{ m ox-nominal}$    | Various                      |

| Phase I/EBL                                     | 10                     | 0                       | 2000                                | 10 000                                          | $3.5 \times 10^{12}$              | 650                                                              | $C_{	ext{ox-nominal}}$ | 10 nm Ox. w/DCE <sup>a</sup> |

| Phase I/EBL/<br>forming gas                     | 10                     | 0                       | 6600                                | 10 000                                          | $2.4 \times 10^{12}$              | 3500                                                             | $C_{	ext{ox-nominal}}$ | 10 nm Ox. w/DCE              |

| Phase I/<br>polysilicon etch/Al <sup>b</sup>    | 35                     | 0                       | 150                                 | 13 800                                          | $>4 \times 10^{12}$               | 30                                                               | $C_{	ext{ox-nominal}}$ | 35 nm Ox. w/DCE              |

| Phase I/polysilicon etch/<br>Al/forming gas     | 35                     | 0                       | 5250                                | 13 800                                          | $1.8 \times 10^{12}$              | 750                                                              | Hall                   | 35 nm Ox. w/DCE              |

| Phase I/polysilicon etch/<br>ALD/Al             | 35                     | 60                      | 300                                 | 13 800                                          | $>4 \times 10^{12}$               | 50                                                               | $C_{	ext{ox-nominal}}$ | 35 nm Ox. w/DCE              |

| Phase I/polysilicon etch/<br>ALD/Al/forming gas | 35                     | 60                      | 8300                                | 13 800                                          | $1 \times 10^{12}$                | 6800                                                             | Hall                   | 35 nm Ox. w/DCE              |

| Phase I/ebeam Al                                | 35                     | 0                       | 4950                                | 14 250                                          | $2 \times 10^{12}$                | 2500                                                             | $C_{	ext{ox-nominal}}$ | 35 nm Ox. w/DCE              |

| Phase I/ebeam Al/<br>forming gas                | 35                     | 0                       | 8700                                | 14 250                                          | $1.2 \times 10^{12}$              | 5700                                                             | $C_{	ext{ox-nominal}}$ | 35 nm Ox. w/DCE              |

| Phase I/thermal Al                              | 35                     | 0                       | 8000                                | 8000                                            |                                   |                                                                  |                        |                              |

<sup>&</sup>lt;sup>a</sup>DCE—(Dichloroethane).

were characterized by examining changes in either mobility or charge defect density. High-frequency and quasistatic capacitance-voltage (C-V) were used to measure static oxide charge density and interface trap density.

Low-temperature mobilities (T=4.2 K) were measured in test structures that simulated the process steps of the device fabrication. Initial (phase I only) peak mobilities were as high as 16 000 cm<sup>2</sup>/Vs, with a wafer to wafer variability noted in Table I. The experiments described in Table I include a mobility measurement of the phase I and mobility measurements of duplicate samples after each indicated phase II process step. The mobility measurements highlight that: (1) damage to the active region can occur despite an overlying protective layer of polysilicon, notably during EBL, which is a workhorse lithographic method of the quantum-dot community; (2) mobilities can be very low  $(\sim 200 \text{ cm}^2/\text{Vs})$  after steps such as polysilicon etch; (3) forming-gas anneals are critical, and enable the recovery of a significant fraction of the mobility but are not sufficient to recover the entire mobility; and (4) gate stacks most like the quantum dots with the lowest disorder in Sec. II show a mobility of 8300 cm<sup>2</sup>/Vs. The damage from the EBL is presumably a result of secondary photon emission (e.g., x rays) due to the stopping of the impinging high-energy electrons, <sup>39,40</sup> which penetrate the polysilicon and affect the underlying gate oxide and silicon. Although similar qualitative observations about process damage and forming-gas annealing exist in previous literature, few reports exist that describe the process effect on low-temperature mobility that is a commonly used figure of merit for low-temperature devices. In Sec. II, correlation of these mobilities with the quantum-dot behavior leads to the observation of singleperiod Coulomb blockade in samples with both low and high mobility. While the higher mobility device does indeed display superior performance, it is clear that mobility alone is not a sufficient indicator of the ability to form tunnel barriers and quantum dots that exhibit single-period Coulomb blockade consistent with a lithographically defined dot, in contrast to quantum dots formed by local trapping or a disorder potential.

The relative change in interface trap density  $D_{\rm it}$  was also examined for several conditions similar to the device processing in an effort to find processes that minimize both  $D_{\rm it}$  and  $Q_{\rm fb}$  (Table II). Details about the  $D_{\rm it}$  measurements are provided in Appendix B. Forming-gas anneals are known to be critical in reducing  $D_{\rm it}$  (Refs. 39 and 40) as well as recovering mobility. After forming-gas annealing, little variation in the reduced  $D_{\rm it}$  is observed for the different process steps. Because  $D_{\rm it}$  and near interface traps are correlated with both 1/f noise and paramagnetically active defects, it is an important observation that the nanostructure fabrication steps do not introduce more of these harmful defects.

The flat-band voltage  $V_{\rm fb}$  was monitored for the different processing conditions, to examine the change in effective net charge in the oxide (Table II). A shift in  $V_{\rm fb}$  can be associated with a change in the sum of positive and negative charge in the oxide stack. For unprocessed thermal gate oxides, it is known that a large positive fixed charge resides near the oxide-Si interface.  $Q_{\rm fb}$  is the charge calculated from the difference between the measured flat-band voltage shift and the theoretical ideal case with a charge-free oxide. The charge at the oxide-Si interface that accounts for the observed flat-band shift in each case investigated is reported in Table II. Process damage can distribute either negative or positive charge throughout the oxide, with charge closer to the top metal gate contributing less of an offset than that nearer to

<sup>&</sup>lt;sup>b</sup>Unless noted, aluminum deposited via electron-beam evaporation.

$D_{\text{it-av}}$   $(\text{cm}^2/\text{Vs})$  $T_{\rm Al2O3}$  $T_{\rm SiO2\text{-}meas}$  $D_{\mathrm{it} ext{-lo}}$  $V_{\rm fb}$  $Q_{\mathrm{fb}}$  $T_{\rm SiO2-nominal}$  $(cm^2/Vs) \pm 1 \times 10^{10}$  $(cm^{-2}) \pm 3.2 \times 10^{10}$ Condition (nm) (nm) (nm) (V)  $6.58 \times 10^{10}$ SiO2 a/Al 35 0 35.3  $2.39 \times 10^{10}$  $3.51 \times 10^{10}$ -0.79 $2.88 \times 10^{10}$  $2.71\times10^{10}$  $-1.17 \times 10^{11}$ SiO<sub>2</sub>/15 nm Al<sub>2</sub>O<sub>3</sub>/Al 35 15 35 -0.45 $3.68 \times 10^{10}$  $4.19 \times 10^{10}$  $3.5 \times 10^{10}$ SiO<sub>2</sub>/30 nm Al<sub>2</sub>O<sub>3</sub>/Al 35 30 35 -0.76SiO<sub>2</sub>/polysilicon etch/Al 35 0 8.4 С С  $3-6 \times 10^{12}$ SiO<sub>2</sub>/Al/no FG anneal (Ref. 41) 0 N/A N/A N/A N/A N/A  $8.73\times10^{10}$ SiO<sub>2</sub> b/Al 10 0 10 -0.72 $1.74 \times 10^{10}$  $2.55 \times 10^{10}$  $5.38 \times 10^{10}$ SiO<sub>2</sub>/Al 70 0 70 -0.86 $3.43 \times 10^{10}$  $3.4 \times 10^{10}$  $-2.69 \times 10^{11}$ SiO<sub>2</sub>/polysilicon etch/Al 70 0 44.7 -0.13 $3.32 \times 10^{10}$  $2.98 \times 10^{10}$ SiO<sub>2</sub>/thermal Al 35 0 35 -1.25 $2.71 \times 10^{11}$

TABLE II. Summary of capacitance-voltage test structures simulating device process flow.

the interface, due to screening from the conducting gate.  $Q_{\rm fb}$  is, therefore, an equivalent charge that assumes the charge within the oxide stack is near the interface. We note that mobility is sensitive to the total number of charge centers rather than the net charge.

$Q_{\mathrm{fb}}$  is strongly dependent on the processing choices. The second dielectric thickness, the polysilicon etch, 42 and the method of Al deposition, 43 each impact the effective charge. The magnitudes of the charge densities range from  $\sim$ 5  $\times 10^{10}$  to  $3 \times 10^{11}$  cm<sup>-2</sup>. In the cases where forming-gas anneals are done, the largest contribution to disorder is the fixed charge, which will make a major contribution to the resulting electrostatic disorder potential. Calculations of electrostatic potentials resulting from this range of defects reveal rms fluctuations in the potential comparable to a modulation-doped GaAs/AlGaAs case, as discussed below in Sec. IC. For cases in which no forming-gas anneal is performed, literature reports suggest that the interface trap density can be greater than  $10^{12}$  cm<sup>-2</sup>/eV, well above the measured fixed charge density, and large enough that it would be predicted to produce very deep fluctuations in the potential near the Si interface (Sec. IC).

## B. Device structure and transport measurements

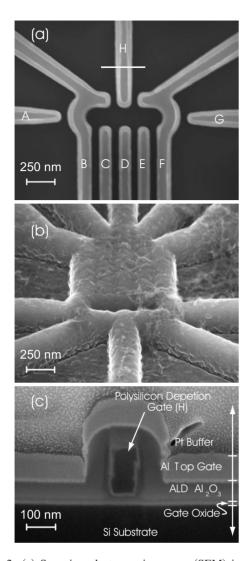

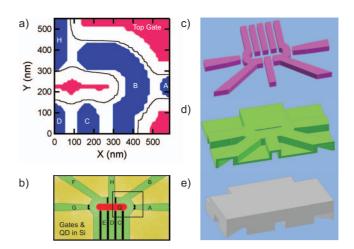

The double-top-gate and open-lateral geometry discussed here provide flexibility in the location of the intended quantum dot relative to the leads and other neighboring nanostructures (e.g., point contacts and neighboring dots). The configuration used in this work is shown in Fig. 2(a). This structure emulates a gate configuration often used for modulation-doped quantum dots and that has successfully been used to form spin qubits by other groups. 3-6 However, in the enhancement-mode MOS structure, a top Al gate overlays the polysilicon depletion gates, as shown in Figs. 2(b) and 2(c), inducing the conduction electrons in the leads and the dot. A 3D capacitance model, described later in this paper, addresses the capacitance matrix of this system and enables an understanding of the quantum-dot size and location.

Transport measurements of two samples (A and B) were performed in a <sup>3</sup>He refrigerator with a base temperature of

250 mK and a third sample (C) was measured in a dilution refrigerator operating at a temperature of 100 mK. Conductance measurements were done using a lock-in amplifier with an ac excitation of 100  $\mu$ V at 13 Hz, unless otherwise noted. Samples A and B are shown to have similar mobilities, 800 and 600 cm²/Vs respectively, but sample B experienced processing known from the work presented in Sec. I to introduce more defects than that experienced by sample A. Sample C experienced processing that produces the lowest defect density of all three samples, and its field mobility is  $\sim$ 4500 cm²/Vs. Additional information about the differences in sample fabrication can be found in Appendix A.

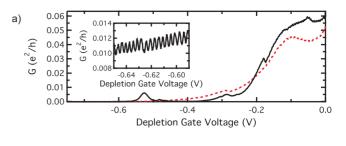

The structure shown in Fig. 2(a) has a central region defined by depletion gates B-F and H that are operated to form a single oval quantum-dot region for devices A and B, and enables tunability through the use of many independent gates. Gates A and G form point contacts with B and F, respectively, and are intended for charge sensing (not discussed here). In spite of similar mobilities between samples A and B, the pinch-off curves for point contacts formed in these two devices, shown in Figs. 3(a) and 3(b), are distinctly different: sample A shows a pinch-off curve with relatively low disorder. The pinch-off curves show a small number of resonances that are probably due to a combination of backscattering,<sup>44</sup> a parasitic dot,<sup>35</sup> and quantum interference. 45 In contrast, sample B shows dramatic evidence of disorder in the form of resonances throughout pinch off of various magnitudes and periods, likely indicating the sustained presence of one or more parasitic dots within the channel. The magnitude and frequency of scattering and trapping in such a defect rich tunnel barrier make it exceptionally difficult to observe single-period Coulomb blockade, consistent with a lithographically formed dot, over any range of bias in sample B.

The inset of Fig. 3(a) shows representative conductance measurements through the quantum dot. Periodic Coulomb-blockade oscillations with similar peak heights are observed. Coulomb-blockade oscillations were visible when sweeping any of the gates immediately adjacent to the quantum dot. In addition to periodic Coulomb oscillations, a noticeable de-

<sup>&</sup>lt;sup>a</sup>Oxides grown in oxygen ambient at 1 atm with a temperature of 1000 °C.

<sup>&</sup>lt;sup>b</sup>10 nm oxide grown in 10% oxygen partial pressure diluted with Ar at 1000 °C.

<sup>&</sup>lt;sup>c</sup>Measurements unattainable due to oxide leakage current. See Appendix B for details.

FIG. 2. (a) Scanning electron microscope (SEM) image of Si nanostructure without  $Al_2O_3$  or Al top gate; (b) tilted SEM image of completed device with both  $Al_2O_3$  and Al top gate; and (c) SEM cross section after focused ion-beam cut of a completed device through gate H at the position shown by the solid horizontal line in (a).

crease in overall conduction (both the maxima and the minima of the peaks) is observed as  $V_{\rm D}$  becomes increasingly negative in the inset of Fig. 3(a). This decrease is due to capacitive coupling between gate D and the entrance and exit tunnel barriers.

In addition to the modest difference in mobility, there are three important differences between samples A and B. First, the feature sizes of sample B are much larger, with gap sizes of 150 nm as opposed to 50 nm or smaller, resulting in much larger pinch-off voltages and a longer effective length for the point contact. Second, the polysilicon depletion gates of sample B were not subject to an additional oxidation after the pattern etch. Finally, at no point during the processing of sample B was a forming-gas anneal performed. Because sample B was subjected to neither a second oxidation nor a forming-gas anneal, both structural and charge-based damage incurred during phase II processing remain as potential sources of disorder. The contrast in character of Figs. 3(a)

FIG. 3. (Color) (a) Transport through point contacts in sample A; conduction is plotted as a depletion gate voltage is applied to both gates B and H (solid trace) and gates F and H (dotted trace) with a top-gate voltage of  $V_{\rm TG}$ =25 V and an applied ac source-drain voltage of 100  $\mu$ V. Inset: transport through the gated quantum dot shown in Fig. 2(a) as a function of  $V_{\rm D}$  showing small amplitude Coulomb-blockade oscillations  $V_{\rm T}$ =25 V,  $V_{\rm B}$ = $V_{\rm F}$ =0,  $V_{\rm H}$ =-100 mV, and  $V_{\rm C}$ = $V_{\rm E}$ =-500 mV. (b) Transport through a point contact in sample B, which was fabricated without a forminggas anneal; conduction is plotted as a depletion gate voltage is applied to both gates A and B with a top gate voltage of  $V_{\rm TG}$ =8 V and an applied ac source-drain voltage of 100  $\mu$ V. Instead of a monotonic decrease in conduction, disorder within the channel produces resonances through pinch-off characteristic of the formation of quantum dots within the constriction.

and 3(b) suggests that additional anneals reduce the number of defects that can lead to scattering or parasitic dot formation, which correlates well with the observed reduction in oxide charge and interface traps (Sec. I) and indicates that peak mobility alone is not a sufficient measure of the disorder that is relevant for quantum-dot devices.

We now discuss a device, sample C, that was processed using many of the optimizations described above. Measurement of test stacks with these additional changes led to peak mobilities higher than  $8000~\rm cm^2/Vs$ , approaching the baseline values obtained immediately after phase I processing. The mobility measured in the field of sample C was  $4500\pm500~\rm cm^2/Vs$ . While not as high as the test structure, this final device mobility is an improvement upon the mobilities of samples A and B.

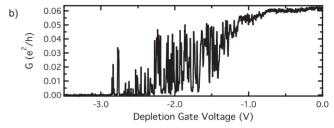

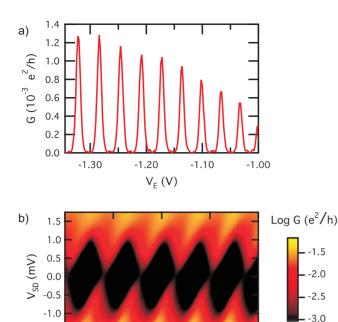

Single quantum dots were observed in the sample C structure on both the left (gates B, C, D, and H) and right (gates D, E, F, and H) portions of this nanostructure, demonstrating the flexibility of the double-layer gate design. Representative data is presented here on a single dot defined on the right side of the structure depicted in Fig. 2(a). The electronic configuration included setting  $V_{\rm B}{=}V_{\rm C}{=}{+}1.5\,$  V to allow unrestricted conduction beneath gates B and C. Tunnel barriers were formed with gate pairs D and H, as well as F and H while gate E was used as a plunger gate and was minimally coupled to either tunnel barrier. As shown in Fig. 4(a), stable

-1.5

-1.30

-1.25

FIG. 4. (Color) (a) Conductance as a function of the voltage on gate E through the quantum dot, formed by gates D, E, F, and H shown in Fig. 2(a). The voltages on the remaining gates are  $V_{\rm Top~Gate}$ =+5 V,  $V_{\rm D}$ =-800 mV,  $V_{\rm F}$ =-2.3 V, and  $V_{\rm H}$ =-900 mV. (b) Conductance as a function of source-drain voltage and the voltage on gate E. Voltages on the remaining gates are  $V_{\rm Top~Gate}$ =+5 V,  $V_{\rm D}$ =-800 mV,  $V_{\rm F}$ =-2.1 V, and  $V_{\rm H}$ =-900 mV.

-1.20

$V_{F}(V)$

-1.15

-1.10

Coulomb blockade was observed at and around the following voltage conditions:  $V_{\text{Top Gate}}$ =+5 V,  $V_{\text{D}}$ =-800 mV,  $V_{\text{E}}$ =-1.25 V,  $V_{\text{F}}$ =-2.3 V, and  $V_{\text{H}}$ =-900 mV. Importantly, as a result of the processing modifications described above, the Si/SiO<sub>2</sub> interface and surrounding dielectric regions were clean enough to allow well-separated peaks with essentially zero conductance in between the Coulomb peaks. An envelope modulation in the Coulomb-blockade peak amplitude is observed in the Coulomb-blockade oscillations as a function of gate voltage. Coulomb-blockade amplitude envelope modulation has been observed in many other semiconductor quantum-dot systems and has been attributed to a variety of sources, including changes in coupling to the leads as orbitals are filled, quantum chaos, universal conductance fluctuations, and variations in tunnel-barrier conductances due to either capacitive crosstalk or disorder. Figure 4(b) shows measurements of Coulomb diamonds in this device. The differential conductance was measured using a lock-in technique with a source-drain voltage  $V_{\rm SD}$  modulated at 13 Hz with an excitation of 50  $\mu$ V. The Coulomb diamonds indicate a charging energy  $E_{\rm C} \approx 1.1$  meV for this quantum dot.

## C. Discussion and analysis

To establish whether the observed quantum-dot behavior was consistent with confinement due to the lithographic gates, in contrast with smaller disorder dots, capacitances for

FIG. 5. (Color) (a) Results of an electrostatic simulation of a quantum-dot structure similar to that shown in Fig. 2(a). Blue regions in the figure represent depletion gates, magenta regions correspond to areas where the metallic top gate comes within a vertical distance of 95 nm of the Si-SiO<sub>2</sub> interface, as noted. The locations of the 2DEG leads and the quantum dot are shown using a black contour marking the conduction edge. (b) Gate labels and representative meshing for 3D capacitance modeling. The area indicated by the black box corresponds to the portion of the device modeled in (a). (c), (d), and (e) 3D rendering of the doped polysilicon depletion gate layer, the dielectric layer, and the metallic top-gate layer, respectively, used in the 3D capacitance modeling. The results of which are shown in Table III.

the quantum-dot structure were calculated numerically and compared to experimental results. A combination of commercial simulation packages were used to calculate the capacitance network of the 3D structure. The initial step was to solve for the potential and charge distribution in the quantum-dot region using a technology computer-assisted design (TCAD) package, Davinci, results of which are shown within Fig. 5(a) for the same gate bias as was used for the transport measurement shown in the inset of Fig. 3(a). A contour of constant electron density  $1.5 \times 10^{11}$  cm<sup>-2</sup> is shown in Fig. 5(a) and was used to define the metallic edge of the quantum dot. An electron density of approximately  $1.5 \times 10^{11}$  cm<sup>-2</sup> has been observed to show a metal-insulator transition at ~100 mK for MOSFETs with mobilities of  $\sim 10~000~\text{cm}^2/\text{Vs.}^{47}$  The edge of this density contour was used to define the geometry of a metal sheet, shown in Fig. 5(b), for a 3D finite elements calculation of the capacitive coupling to the depletion gates. The 3D structure was constructed from the 2D computer-assisted design mask levels and nominal layer thicknesses, Figs. 5(c)-5(e). Table III shows the capacitances calculated with CFD-ACE+, a multiphysics software package from ESI Group. These capacitances are compared to experimental values obtained from device A, measured by monitoring the period of Coulombblockade oscillations as each specific depletion gate voltage is changed. The modeled capacitances are in good agreement with the experimental values, both in magnitude and trend, consistent with the interpretation that the measured quantum dots are defined by the lithographic features of the tunable gated structure rather than by a disorder potential.

Defect charges at or near the oxide-Si interface can contribute to disorder by forming random fluctuation potentials

TABLE III. Calculated and measured capacitances from quantum-dot sample A.

| Gate | Modeled capacitance (aF) | Measured capacitance (aF) |

|------|--------------------------|---------------------------|

| B-Q  | 40.2                     | 48.1                      |

| C-Q  | 16.4                     | 14.7                      |

| D-Q  | 16.9                     | 11.2                      |

| E-Q  | 16.4                     | 14.1                      |

| F-Q  | 40.2                     | 48.1                      |

| H-Q  | 16.7                     | 20.8                      |

deep enough to trap or scatter electrons. Having measured a range of defect densities in the oxide, the dependence of the average magnitude of the disorder potential can be calculated for this range to offer insight about whether the higher range of measured charge densities could contribute sufficiently to explain the disorder in sample A, in contrast with other possible contributions to the disorder such as surface roughness. In particular, over some bias ranges the peaks in the disordered barriers in Fig. 3(b) are equally spaced, indicative of many-electron parasitic dot formation, and inconsistent with trapping from single isolated positive charges in the oxide. The latter would be expected to bind no more than a few electrons, in analogy with an ionized donor in silicon with a confining potential of  $\sim 40-50$  meV.

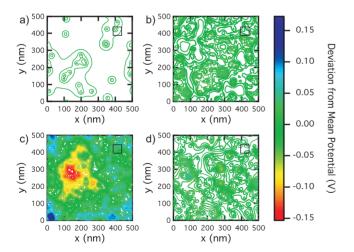

Numerical simulations of the potential produced by a random distribution of bare positive charges located within the oxide and 2 nm from a Si-oxide interface are shown for values of  $1\times10^{10}$  cm<sup>-2</sup>,  $1\times10^{11}$  cm<sup>-2</sup>, and  $1\times10^{12}$  cm<sup>-2</sup> in Figs. 6(a)–6(c), assuming the centroid of the electron distribution is  $\sim$ 5 nm from the interface. The case where the

FIG. 6. (Color) A simulation of bare potential with random distribution of charges located within the oxide, 2 nm from the Si-SiO $_2$  interface with a charge density of (a)  $1\times 10^{10}~{\rm charges/cm^2}$ , (b)  $1\times 10^{11}~{\rm charges/cm^2}$ , (c)  $1\times 10^{12}~{\rm charges/cm^2}$ , and (d) +5  $\times 10^{10}~{\rm charges/cm^2}$  combined with  $-5\times 10^{10}~{\rm charges/cm^2}$  for a net zero charge at the interface. Contour spacing in each plot is 6 mV. Boxes represent a guide for an area of approximately 50 nm  $\times 50~{\rm nm}$  representative of dimensions approximately the size of the point-contact dimension.

net charge is zero through the introduction of both positive and negative charge densities of magnitude  $5 \times 10^{10}$  cm<sup>-2</sup> (a total to  $1 \times 10^{11}$  cm<sup>-2</sup> scattering centers) is also shown in Fig. 6(d), demonstrating the effect of compensating negative charge on the disorder potential. An image charge solution was used to calculate the potential in the silicon due to a charge in the oxide, 48 using a dielectric constant of 11.9 for silicon and 3.9 for silicon dioxide. The standard deviation of the potentials summed over 20 different ensembles was calculated to be 4.3, 13.6, 42.0, and 13.5 meV for 10<sup>10</sup>, 10<sup>11</sup>,  $10^{11}$ , and  $-5 \times 10^{10}$  cm<sup>-2</sup> +  $5 \times 10^{10}$  cm<sup>-2</sup> charge densities with maximum well depths of 40.7, 201, 1630, and 48.0 meV, respectively, where the variance in charge position leads to clusters of charge with significantly deeper wells. The standard deviation in a high mobility modulation-doped GaAs/AlGaAs structure with 2.16×10<sup>12</sup> cm<sup>-2</sup> ionized donors at a distance of 28 nm, for comparison, was calculated by Nixon and Davies<sup>49</sup> to be 18 mV, which falls within the range of 10<sup>11</sup> and 10<sup>12</sup> cm<sup>-2</sup> fixed charge at the Si/SiO<sub>2</sub> interface.

## II. SUMMARY

Single-period Coulomb blockade, consistent with the charging energy of a lithographically formed quantum dot, is observed in two Si structures that have an open-lateral MOS enhancement-mode gate geometry. The open-lateral gate geometry allows significant tuning of the confining potential and emulates structures in GaAs/AlGaAs and sSi/SiGe that have been used to achieve few electron double quantum dots and probe coherent few electron-spin properties. Stable dot formation in several different configurations (i.e., left, right, or both sides of a double-dot structure) is demonstrated showing the flexible tuning of the position of the dots in the open-lateral geometry. Achievement of low disorder quantum dots in an open-lateral enhancement-mode MOS geometry is motivated by potential benefits such as more tunable electron density, integration for enhanced read out, reduced background dopants, and potential hybrid donor quantum-dot coupling.

Disorder due to defects introduced during processing is found to be a critical hurdle to achieving quantum dots that are not plagued by scattering and parasitic dot formation. Characterization of each process flow step's effect on mobility and charging of the oxides through high- and lowfrequency capacitance-voltage measurements were described. The primary change in process-induced charging of the oxides is in fixed charge in the oxide while the interface trap density can be maintained near the same values as the starting gate oxide-silicon interface. Improved processing leads to a transition from a device that is plagued by disorder to one that shows clean quantum-dot behavior over wide bias ranges. The open geometry is also used to form tunable dots in several configurations, consistent with using different lithographic gates to define the dot size rather than being dominated by disorder potentials. Single-period Coulombblockade behavior is achieved in process flows that are characterized to have mobilities that range from 500 to 4000 cm<sup>2</sup>/Vs,  $D_{it} \sim 3 \times 10^{10}$  cm<sup>-2</sup> eV<sup>-1</sup>, and  $Q_{fb} \sim 3.5$   $\times 10^{11}~{\rm cm^{-2}}$ , where  $Q_{\rm fb}$  is a net charge density of positive and negative charges combined. These charge densities correspond to an rms electrostatic potential near the Si interface that is comparable in order of magnitude to a representative GaAs/AlGaAs modulation-doped structures.

## **ACKNOWLEDGMENTS**

The authors are grateful for sample preparation done by D. Tibbets. The authors would also like to thank N. Bishop and E. Bielejec for reviewing the manuscript and helpful discussions. This work was performed, in part, at the Center for Integrated Nanotechnologies, a U.S. DOE, Office of Basic Energy Sciences user facility. The work at both Sandia National Laboratories and the University of Wisconsin was supported by the Sandia National Laboratories Directed Research and Development Program. Sandia National Laboratories is a multiprogram laboratory operated by Sandia Corporation, a Lockheed-Martin Co., for the U.S. Department of Energy under Contract No. DE-AC04-94AL85000.

## APPENDIX A

Phase I fabrication steps: (1) source-drain implant: 2  $\times 10^{15}$  cm<sup>-2</sup> arsenic implanted at an energy of 50 keV. (2) Gate oxidation: 35 nm SiO<sub>2</sub> grown at 900 °C for 150 min. (3) Silicon deposition: 200 nm nominally undoped amorphous silicon (a-Si). (4) a-Si doping:  $5 \times 10^{15}$  cm<sup>-2</sup> arsenic implanted at an energy of 35 keV. (5) a-Si patterning etch: CF<sub>4</sub>-based plasma etch through ~80% of the layer followed by a high selectivity HBr etch to stop on the SiO<sub>2</sub> gate oxide. (6) a-Si oxidation, crystallization, and activation: 10 nm SiO<sub>2</sub> grown for 13 min at 900 °C and 30 min N2 anneal at 900 °C. (7) Field-oxide deposition: 300-500 nm SiO<sub>2</sub> deposited via high-density plasma chemical vapor deposition. (8) Via formation: CF<sub>4</sub>-based plasma etch. (9) Via, bond pad metallization: 200 Å Ti, 500 Å Ti/N, 5000 Å tungsten conformally deposited via chemical vapor deposition. (10) Oxide window opening: CF<sub>4</sub>-based plasma etch.

Phase II fabrication steps for samples A and B: (1) e-beam lithography: 100 keV electron beam with 400 pA beam current and areal dose of 190  $\mu$ C/cm<sup>2</sup> on negative e-beam resist (NEB). (2) Nitride/oxide etch: 440 s, CHF<sub>3</sub>-based, 350 W, inductive-coupled plasma reactive-ion etch (ICP-RIE). (3) Depletion gate formation, polysilicon etch: 170 s, HBr, 300 W ICP-RIE with exposed and developed NEB as etch mask. (4) NEB removal: solvent clean and 20 min oxygen ash. (5) Preoxidation clean: 15 min tungsten etch in 60 °C H<sub>2</sub>O<sub>2</sub>, 5 min nitride etch in 165 °C H<sub>3</sub>PO<sub>4</sub>, RCA Clean.<sup>50</sup> (6) Thermal oxidation (device A only): 24 min thermal oxidation at 900 °C. (7) Secondary oxide deposition: 200 °C ALD of 60 nm of Al<sub>2</sub>O<sub>3</sub> using trimethylaluminum and water (H<sub>2</sub>O) precursor chemistry. (8) ALD via etch: Patterned HF via etch to ohmic and polysilicon contacts through ALD Al<sub>2</sub>O<sub>3</sub>. (9) Top-gate bonding pad metallization: 1000 Å Al deposited via e-beam evaporation. (10) Forming-gas anneal (device A only): 30 min at 400 °C (10% H<sub>2</sub>).

Phase II fabrication steps for sample C: (1) e-beam lithography: 100 keV electron beam with 400 pA beam current and

areal dose of 190  $\mu$ C/cm<sup>2</sup> on negative e-beam resist NEB. (2) Nitride/oxide etch: 440 s, CHF<sub>3</sub>-based 350 W, ICP-RIE. (3) NEB removal: solvent clean. (4) Depletion gate formation, polysilicon etch: 170 s, HBr, 300 W ICP-RIE with exposed and developed NEB as etch mask. (5) Preoxidation clean: 15 min tungsten etch in 60 °C H<sub>2</sub>O<sub>2</sub>, 5 min nitride etch in 165 °C H<sub>3</sub>PO<sub>4</sub>, RCA Clean. (6) Thermal oxidation: 24 min thermal oxidation at 900 °C. (7) Secondary oxide deposition: 200 °C ALD of 60 nm of Al<sub>2</sub>O<sub>3</sub> using trimethylaluminum and water (H<sub>2</sub>O) precursor chemistry. (8) Forming-gas anneal: 30 min at 450 °C (10% H<sub>2</sub>). (9) Topgate metallization: 1000 Å Al deposited globally via e-beam evaporation. (10) Top-gate formation: top-gate patterned and formed using MIF 319 developer as an Al etchant. (11) ALD via etch: patterned HF via etch to ohmic and polysilicon contacts through ALD Al<sub>2</sub>O<sub>3</sub>. (12) Bonding pad metallization: bond pads patterned, 1000 Å Al deposited via e-beam evaporation. (13) Final forming-gas anneal: 30 min at 400 °C (10% H<sub>2</sub>).

## APPENDIX B

C-V measurements were performed on experimentally simulated gate stacks for this work. Phase I material was not used because of parasitic capacitances and the high resistance of the substrates, which is problematic for high-frequency C-V measurements. The starting substrates used in this study were p-type epitaxial Si on  $p^+$  substrates. Thermal gate oxides were grown at 1000 °C and annealed in nitrogen at 1000 °C for 15 min.

A near midgap interface trap density,  $D_{\text{it-lo}}$ , an average interface trap density,  $D_{\text{it-av}}$ , and  $Q_{\text{fb}}$  are reported in Table II for the different cases examined.  $D_{it}$  is reported at the lowest capacitance  $(C_{lo})$  during the low-frequency sweep as  $D_{it-lo}$ .  $D_{\text{it-av}}$  is an average value of  $D_{\text{it}}$  between the Fermi level and weak inversion. The uncertainty of  $D_{\rm it}$  for values around midgap as indicated in the table are dominated by a confidence of ~2 pF in the total capacitance value. The uncertainty for  $D_{\text{it-lo}}$  is estimated to be  $1 \times 10^{10}$  cm<sup>-2</sup> eV<sup>-1</sup>. The uncertainty in  $Q_{\mathrm{fb}}$  arises from an uncertainty in the workfunction difference between the metal and the silicon ohmic contact, which is dependent on deposition conditions. For this work, the work-function difference for e-beam deposited Al was measured to be 4.43 V determined from the flat-band voltage dependence on oxide thickness and the uncertainty in that work function leads to a  $3.2 \times 10^{10}$  cm<sup>-2</sup> uncertainty in  $Q_{\mathrm{fb}}$ .51

We note that in the etch experiment some of the oxide was lost during the polysilicon etch leading to a thinner oxide, as noted in Table II. The experiment was done for both 35 and 70 nm thicknesses. Within the uncertainty of the measurement,  $D_{\rm it}$  both before the etches and after the etches with a subsequent forming-gas anneal is indistinguishable for the 70 nm case. Leakage through the thinned 35 nm oxide led to inaccurate C-V curves for that case.  $D_{\rm it-lo}$  of samples with 15 and 30 nm of ALD Al<sub>2</sub>O<sub>3</sub> have a  $D_{\rm it-lo}$  of  $2.9\times10^{10}$  and  $3.7\times10^{10}$ , respectively. The increase in  $D_{\rm it-lo}$  is within the uncertainty of the measurement and therefore is not considered meaningful.

- <sup>1</sup>D. Loss and D. P. DiVincenzo, Phys. Rev. A **57**, 120 (1998).

- <sup>2</sup>D. P. DiVincenzo, Fortschr. Phys. **48**, 771 (2000).

- <sup>3</sup> J. M. Elzerman, R. Hanson, L. H. W. van Beveren, B. Witkamp, L. M. K. Vandersypen, and L. P. Kouwenhoven, Nature (London) 430, 431 (2004).

- <sup>4</sup>J. R. Petta, A. C. Johnson, J. M. Taylor, E. A. Laird, A. Yacoby, M. D. Lukin, C. M. Marcus, M. P. Hanson, and A. C. Gossard, Science 309, 2180 (2005).

- <sup>5</sup>F. H. L. Koppens, C. Buizert, K. J. Tielrooij, I. T. Vink, K. C. Nowack, T. Meunier, L. P. Kouwenhoven, and L. M. K. Vandersypen, Nature (London) 442, 766 (2006).

- <sup>6</sup>M. Pioro-Ladriere, Y. Tokura, T. Obata, T. Kubo, and S. Tarucha, Appl. Phys. Lett. **90**, 024105 (2007).

- <sup>7</sup>L. P. Kouwenhoven, C. M. Marcus, P. L. McEuen, S. Tarucha, R. M. Westervelt, and N. S. Wingreen, in *Mesoscopic Electron Transport*, edited by L. L. Sohn, L. P. Kouwenhoven, and G. Schön (Kluwer, New York, 1997), Vol. 345, p. 105.

- <sup>8</sup>L. P. Kouwenhoven and C. M. Marcus, Phys. World **11** (6), 35 (1998).

- <sup>9</sup>W. Van Der Wiel, T. Fujisawa, S. Tarucha, and L. P. Kouwenhoven, Rev. Mod. Phys. **75**, 1 (2002).

- <sup>10</sup>M. Ciorga, A. S. Sachrajda, P. Hawrylak, C. Gould, P. Zawadzki, S. Jullian, Y. Feng, and Z. Wasilewski, Phys. Rev. B 61, R16315 (2000).

- <sup>11</sup> J. M. Elzerman, R. Hanson, J. S. Greidanus, L. H. Willems van Beveren, S. De Franceschi, L. M. K. Vandersypen, S. Tarucha, and L. P. Kouwenhoven, Phys. Rev. B 67, 161308(R) (2003).

- <sup>12</sup>D. Schröer, A. D. Greentree, L. Gaudreau, K. Eberl, L. C. L. Hollenberg, J. P. Kotthaus, and S. Ludwig, Phys. Rev. B 76, 075306 (2007).

- <sup>13</sup>J. M. Taylor, H. A. Engel, W. Dur, A. Yacoby, C. M. Marcus, P. Zoller, and M. D. Lukin, Nat. Phys. 1, 177 (2005).

- <sup>14</sup>D. J. Reilly, J. M. Taylor, J. R. Petta, C. M. Marcus, M. P. Hanson, and A. C. Gossard, Science **321**, 817 (2008).

- <sup>15</sup>B. E. Kane, Nature (London) **393**, 133 (1998).

- <sup>16</sup>R. Vrijen, E. Yablonovitch, K. Wang, H. W. Jiang, A. Balandin, V. Roychowdhury, T. Mor, and D. DiVincenzo, Phys. Rev. A 62, 012306 (2000).

- <sup>17</sup>M. Friesen, P. Rugheimer, D. E. Savage, M. G. Lagally, D. W. van der Weide, R. Joynt, and M. A. Eriksson, Phys. Rev. B 67, 121301(R) (2003).

- <sup>18</sup>F. Simmel, D. Abusch-Magder, D. A. Wharam, M. A. Kastner, and J. P. Kotthaus, Phys. Rev. B 59, R10441 (1999).

- <sup>19</sup>S. J. Angus, A. J. Ferguson, A. S. Dzurak, and R. G. Clark, Nano Lett. 7, 2051 (2007).

- <sup>20</sup>H. Liu, T. Fujisawa, H. Inokawa, Y. Ono, A. Fujiwara, and Y. Hirayama, Appl. Phys. Lett. **92**, 222104 (2008).

- <sup>21</sup>L. J. Klein, K. A. Slinker, J. L. Truitt, S. Goswami, K. L. M. Lewis, S. N. Coppersmith, D. W. van der Weide, M. Friesen, R. H. Blick, D. E. Savage, M. G. Lagally, C. Tahan, R. Joynt, M. A. Eriksson, J. O. Chu, J. A. Ott, and P. M. Mooney, Appl. Phys. Lett. 84, 4047 (2004).

- <sup>22</sup>M. R. Sakr, H. W. Jiang, E. Yablonovitch, and E. T. Croke, Appl. Phys. Lett. **87**, 223104 (2005).

- <sup>23</sup>T. Berer, D. Pachinger, G. Pillwein, M. Muhlberger, H. Lichtenberger, G. Brunthaler, and F. Schaffler, Appl. Phys. Lett. 88, 162112 (2006).

- <sup>24</sup>L. J. Klein, D. E. Savage, and M. A. Eriksson, Appl. Phys. Lett. 90, 033103 (2007).

- <sup>25</sup>C. B. Simmons, M. Thalakulam, N. Shaji, L. J. Klein, H. Qin, R.

- H. Blick, D. E. Savage, M. G. Lagally, S. N. Coppersmith, and M. A. Eriksson, Appl. Phys. Lett. **91**, 213103 (2007).

- <sup>26</sup> Y. Hu, H. O. H. Churchill, D. J. Reilly, J. Xiang, C. M. Lieber, and C. M. Marcus, Nat. Nanotechnol. 2, 622 (2007).

- <sup>27</sup> A. Fuhrer, M. Füchsle, T. C. G. Reusch, B. Weber, and M. Y. Simmons, Nano Lett. 9, 707 (2009).

- <sup>28</sup> N. Shaji, C. B. Simmons, M. Thalakulam, L. J. Klein, H. Qin, H. Luo, D. E. Savage, M. G. Lagally, A. J. Rimberg, R. Joynt, M. Friesen, R. H. Blick, S. N. Coppersmith, and M. A. Eriksson, Nat. Phys. 4, 540 (2008).

- <sup>29</sup> H. W. Liu, T. Fujisawa, Y. Ono, H. Inokawa, A. Fujiwara, K. Takashina, and Y. Hirayama, Phys. Rev. B **77**, 073310 (2008).

- <sup>30</sup>E. Hourdakis, J. A. Wahl, and N. Zimmerman, Appl. Phys. Lett. 92, 062102 (2008).

- <sup>31</sup> N. Zimmerman, B. Simonds, A. Fujiwara, Y. Ono, Y. Takahashi, and H. Inokawa, Appl. Phys. Lett. **90**, 033507 (2007).

- <sup>32</sup>N. Zimmerman, W. H. Huber, A. Fujiwara, and Y. Takahashi, Appl. Phys. Lett. **79**, 3188 (2001).

- <sup>33</sup> T. M. Gurrieri, M. S. Carroll, M. P. Lilly, and J. E. Levy, *IEEE-NANO 2008* (IEEE, Dallas, TX, 2008).

- <sup>34</sup> A. Morello, C. C. Escott, H. Huebl, L. H. Willems van Beveren, L. C. L. Hollenberg, D. N. Jamieson, A. S. Dzurak, and R. G. Clark, Phys. Rev. B **80**, 081307(R) (2009).

- <sup>35</sup>G. P. Lansbergen, R. Rahman, C. J. Wellard, I. Woo, J. Caro, N. Collaert, S. Biesemans, G. Klimeck, L. C. L. Hollenberg, and S. Rogge, Nat. Phys. 4, 656 (2008).

- <sup>36</sup>C. Buizert, F. H. L. Koppens, M. Pioro-Ladrière, H. P. Tranitz, I. T. Vink, S. Tarucha, W. Wegscheider, and L. M. K. Vandersypen, Phys. Rev. Lett. **101**, 226603 (2008).

- <sup>37</sup>L. P. Rokhinson, L. J. Guo, S. Y. Chou, and D. C. Tsui, Appl. Phys. Lett. **76**, 1591 (2000).

- <sup>38</sup> H. Ishikuro and T. Hiramoto, Appl. Phys. Lett. **74**, 1126 (1999).

- <sup>39</sup>E. H. Nicollian and J. R. Brews, MOS (Metal Oxide Semiconductor) Physics and Technology (John Wiley and Sons, Hoboken, New Jersey, 2003), p. 781.

- <sup>40</sup>T. P. Ma, in *Ionizing Radiation Effects in MOS Devices and Circuits*, edited by P. V. Dressendorfer and T. P. Ma (John Wiley and Sons, New York, 1989), p. 401.

- <sup>41</sup>G. J. Gerardi, E. H. Poindexter, P. J. Caplan, and N. M. Johnson, Appl. Phys. Lett. **49**, 348 (1986).

- <sup>42</sup> Significant positive shifts in V<sub>fb</sub> and corresponding negative shifts in Q<sub>fb</sub> were also observed after both polysilicon etch and Al<sub>2</sub>O<sub>3</sub> deposition. Negative charge has been previously reported in ALD Al<sub>2</sub>O<sub>3</sub> films on oxide (Ref. 52) which is qualitatively consistent with this result. Also notable is that the V<sub>fb</sub> shift is less positive for the thicker Al<sub>2</sub>O<sub>3</sub> films. The cause of this is unclear, however it seems reasonable that the e-beam damage is depth dependent so the negative charge introduced during the deposition would be located further from the interface for the thicker Al<sub>2</sub>O<sub>3</sub> film, leading to a smaller V<sub>fb</sub> shift. Negative charging of the oxide after reactive ion etching has been reported previously and is also consistent with the results from this study (Ref. 53).

- $^{43}$ A slight positive shift in  $V_{\rm fb}$  is observed for e-beam deposition relative to thermal deposition, leading to a lower net positive charge for the e-beam Al case. Mobility is, however, reduced after e-beam deposition as compared to thermal Al deposition, indicating the presence of more scattering centers. The combination of the mobility measurements and the extracted  $Q_{\rm fb}$  suggests that more negative charge centers are introduced by the

- e-beam deposition than the thermal Al case leading to a lower net positive  $Q_{\rm fb}$  but to more total charge centers in the oxide near the interface. This is consistent with literature reports of damage produced by e beam but not thermal processes (Ref. 40).

- <sup>44</sup>K. Shepard, Phys. Rev. B **44**, 9088 (1991).

- <sup>45</sup> J. A. Katine, M. A. Eriksson, A. S. Adourian, R. M. Westervelt, J. D. Edwards, A. Lupu-Sax, E. J. Heller, K. L. Campman, and A. C. Gossard, Phys. Rev. Lett. **79**, 4806 (1997).

- <sup>46</sup>Three crucial modifications were made. More RCA and HF cleans were introduced into the process, an Al-lift-off process was used for the final top gate, which protected the underlying Al<sub>2</sub>O<sub>3</sub> better and a hard mask was used for the polysilicon etch, which reduced the plasma processing exposure necessary to remove the photoresist. More details are found in Appendix A.

- <sup>47</sup>L. A. Tracy, E. H. Hwang, K. Eng, G. A. Ten Eyck, E. P. Nordberg, K. Childs, M. S. Carroll, M. P. Lilly, and S. Das Sarma,

- Phys. Rev. B 79, 235307 (2009).

- <sup>48</sup>J. D. Jackson, *Classical Electrodynamics* (John Wiley and Sons, New York, 1999), p. 156.

- <sup>49</sup>J. A. Nixon and J. H. Davies, Phys. Rev. B **41**, 7929 (1990).

- <sup>50</sup>RCA clean is two sequential cleans, RCA1: 5:1:1 H<sub>2</sub>O:NH<sub>4</sub>OH:H<sub>2</sub>O<sub>2</sub> at 70 °C for 7 min followed by RCA2: 5:1:1 H<sub>2</sub>O:HC1:H<sub>2</sub>O<sub>2</sub> at 70 °C for 7 min.

- <sup>51</sup>N. Lifshitz, IEEE Trans. Electron Devices **32**, 617 (1985).

- <sup>52</sup>J. Buckley, B. De Salvo, D. Deleruyelle, M. Gely, G. Nicotra, S. Lombardo, J. F. Damlencourt, P. Hollinger, F. Martin, and S. Deleonibus, in *14th Biennial Conference on Insulating Films on Semiconductors* (Elsevier Science Bv, Leuven, Belgium, 2005), p. 210.

- <sup>53</sup>D. Misra and E. L. Heasell, Semicond. Sci. Technol. 5, 229 (1990)